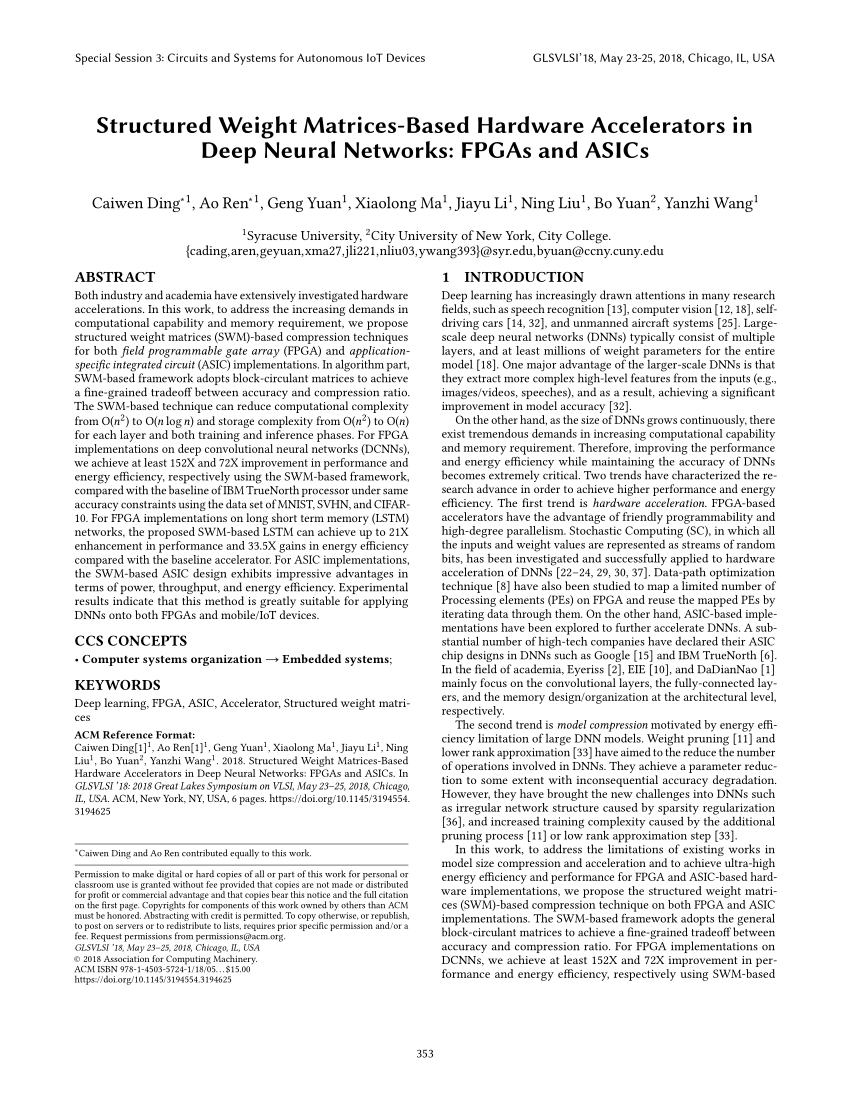

PDF) Structured Weight Matrices-Based Hardware Accelerators in Deep Neural Networks: FPGAs and ASICs

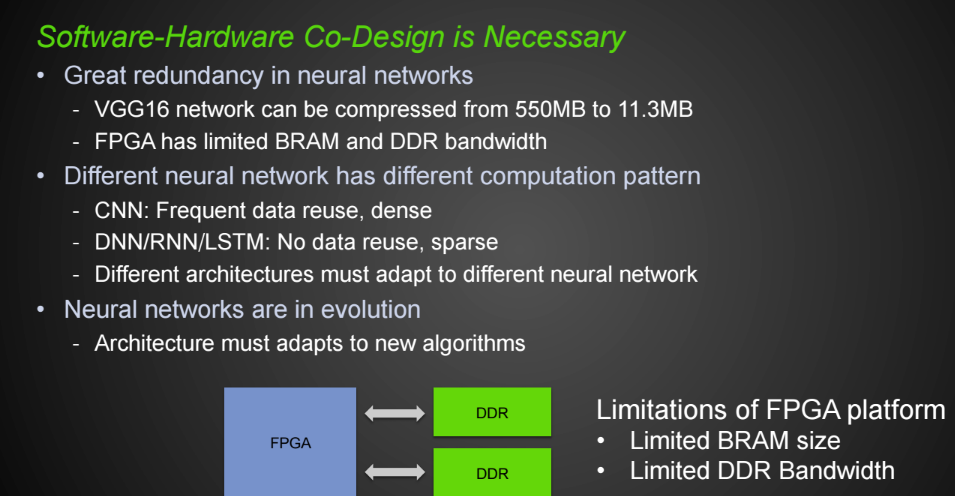

How to Develop High-Performance Deep Neural Network Object Detection/Recognition Applications for FPGA-based Edge Devices - Embedded Computing Design

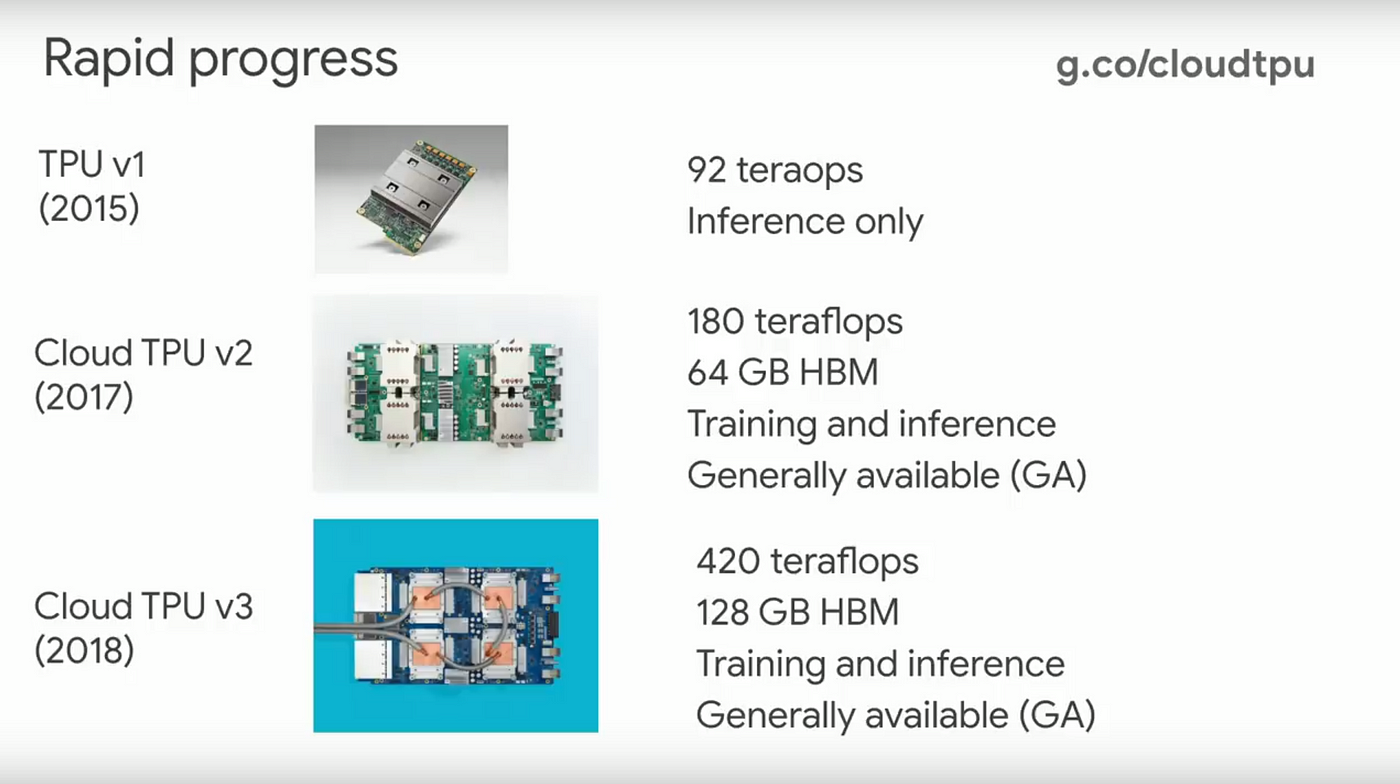

The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com

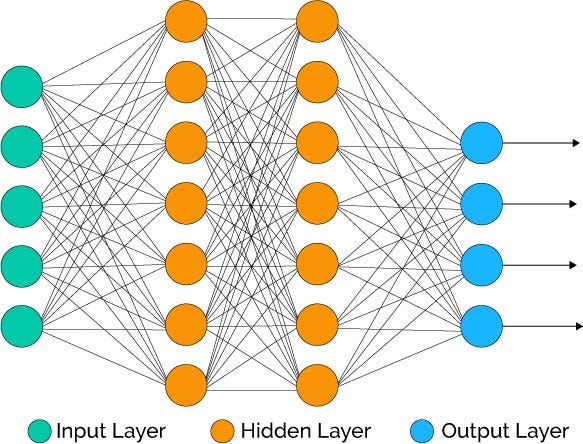

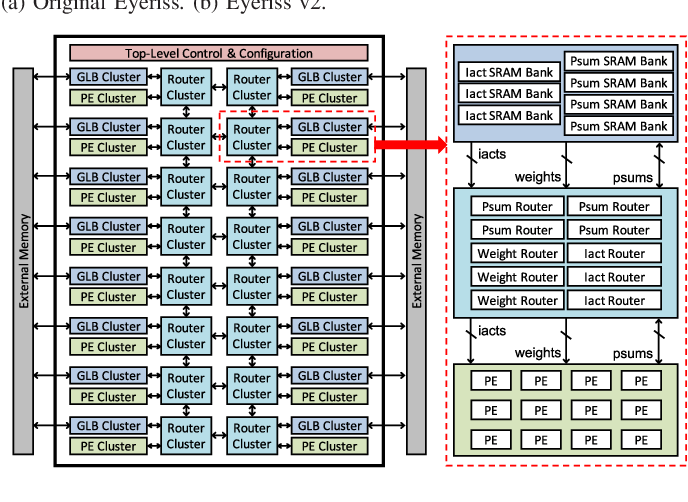

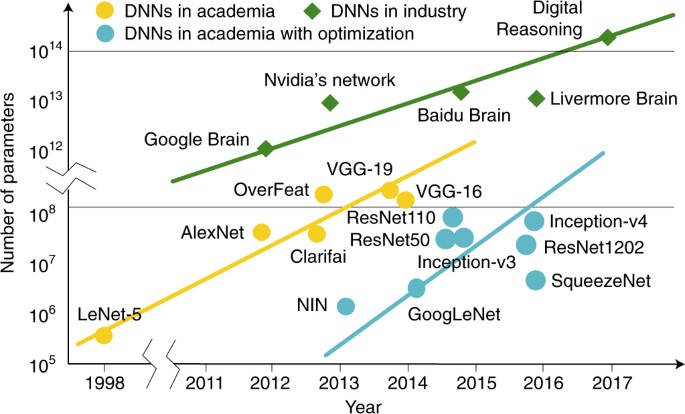

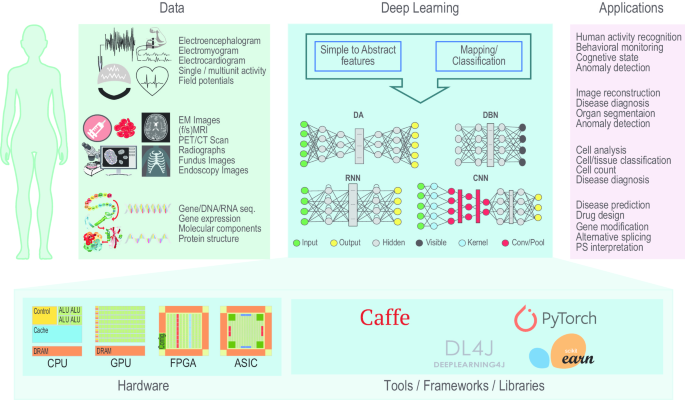

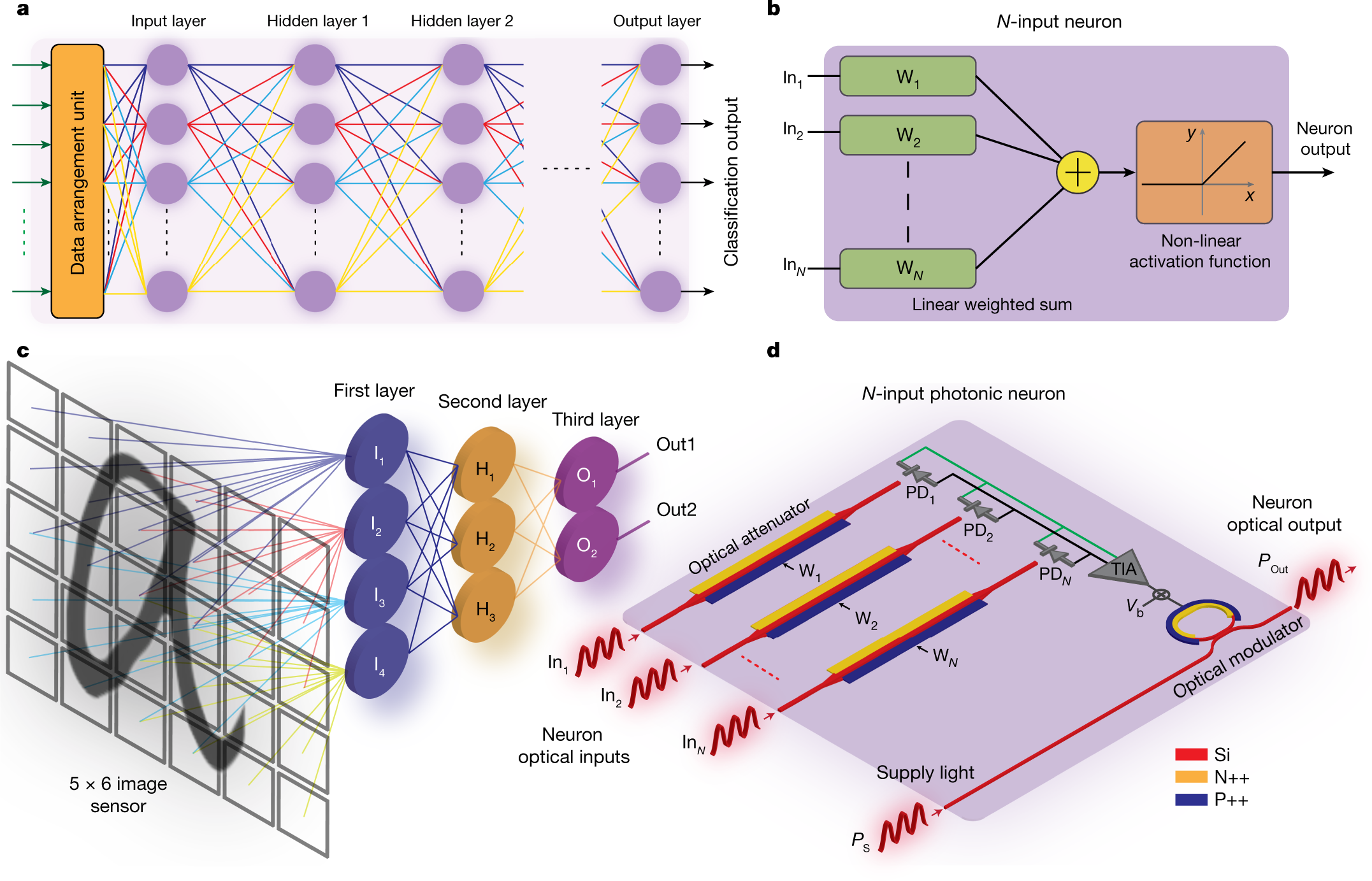

Future Internet | Free Full-Text | An Updated Survey of Efficient Hardware Architectures for Accelerating Deep Convolutional Neural Networks